# UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

# MEDIATEK, INC., Petitioner,

v.

MOSAID TECHNOLOGIES INC., Patent Owner.

> IPR2024-00718 Patent 7,996,811 B2

Before KEN B. BARRETT, JOHN F. HORVATH, and ELIZABETH M. ROESEL, *Administrative Patent Judges*.

Opinion for the Board filed by Administrative Patent Judge BARRETT.

Opinion Concurring filed by Administrative Patent Judge HORVATH.

Opinion Dissenting filed by Administrative Patent Judge ROESEL.

BARRETT, Administrative Patent Judge.

DECISION Denying Institution of *Inter Partes* Review 35 U.S.C. § 314

# I. INTRODUCTION

MediaTek Inc. ("Petitioner")<sup>1</sup> filed a Petition (Paper 2, "Pet.") requesting *inter partes* review of claims 1–74 of U.S. Patent No. 7,996,811 B2 (Ex. 1001, "the '811 Patent"). MOSAID Technologies, Inc. ("Patent Owner")<sup>2</sup> filed a Preliminary Response (Paper 8, "Prelim. Resp.").

We have authority to determine whether to institute an *inter partes* review. 35 U.S.C. § 314 (2018); 37 C.F.R. § 42.4(a) (2023). An *inter partes* review may not be instituted "unless . . . the information presented in the petition . . . and any response . . . shows that there is a reasonable likelihood that the petitioner would prevail with respect to at least 1 of the claims challenged in the petition." 35 U.S.C. § 314(a). Having considered the arguments and evidence presented by Petitioner and Patent Owner, we do not institute an *inter partes* review of the challenged claims.

### II. BACKGROUND

A. Related Matter

The parties identify the following district court action involving the '811 Patent: *MOSAID Technologies Inc. v. MediaTek, Inc.*, No. 2:23-cv-00129-JRG (E.D. Tex.). Pet. 100; Paper 6, 1 (Patent Owner's updated mandatory notices). The parties also identify other, concluded proceedings involving the '811 patent. Pet. 100; Paper 6, 1.

<sup>&</sup>lt;sup>1</sup> Petitioner identifies MediaTek Inc. and MediaTek USA Inc. as real parties in interest. Pet. 99.

<sup>&</sup>lt;sup>2</sup> Patent Owner identifies MOSAID Technologies Inc. as the real party in interest. Paper 6, 1.

### *B. The '811 Patent (Ex. 1001)*

The '811 Patent is titled "Power Managers for an Integrated Circuit" and was issued based on a regular application filed December 11, 2008. Ex. 1001, codes (22), (54). The '811 Patent lists a series of related applications, the earliest of which is a provisional application filed May 7, 2003. *Id.* at code (60). According to the '811 Patent, "[o]ne design goal for integrated circuits is to reduce power consumption." *Id.* at 1:29–30. The '811 Patent states, "[s]ome prior integrated circuits have employed voltage islands or multiple clocks to lower power consumption," but "[o]ne problem with these integrated circuits is that the voltages in the power island and the frequencies of the multiple clocks are static" and "do not dynamically change based on the needs and operation of the integrated circuit." *Id.* at 2:21–26.

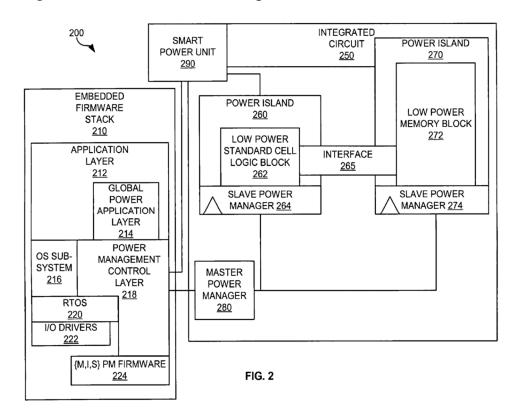

Figure 2 of the '811 Patent is reproduced below.

Figure 2 shows a system for managing power in integrated circuit 250. Ex. 1001, 2:65–67, 4:61–63. The system includes embedded firmware stack 210, which runs on a central processing unit (CPU) and includes application layer 212 and power management control layer (PMCL) 218. *Id.* at 4:63–5:4. Integrated circuit 250 includes power islands 260 and 270, master power manager (MPM) 280, and smart power unit (SPU) 290. *Id.* at 5:5–6, 5:40–43, Fig. 2; *see also id.* at 4:39–43 (explaining acronyms). Power island 260 includes slave power manager (SPM) 264, and power island 270 includes SPM 274. *Id.* at 5:6–9.

According to the '811 Patent, the integrated circuit may be a systemon-a-chip that includes "multiple IP units, which are blocks of circuitry performing specific functions." Ex. 1001, 2:14–17, 3:49–52. The '811 Patent explains that a power island is "any section, delineation, partition, or division of the integrated circuit" within which "power consumption is controlled," and the power islands may be "delineated based on geographic factors of the integrated circuit . . . [or] based on functional IP units of the integrated circuit." *Id.* at 3:59–67.

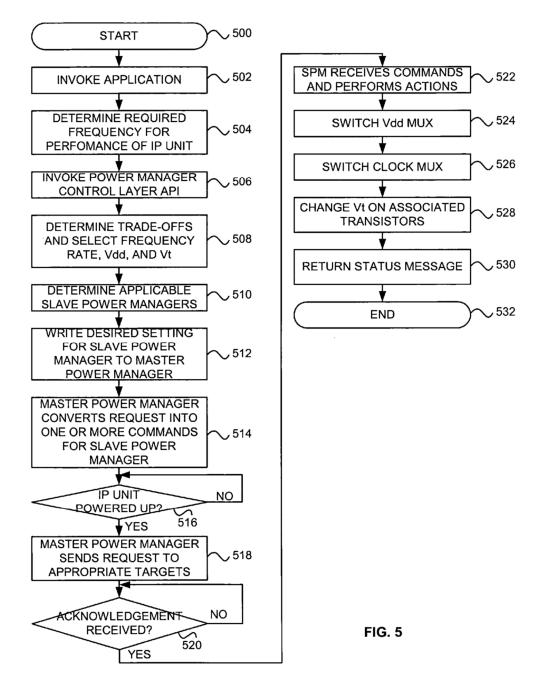

Figure 5 of the '811 Patent is reproduced below.

Figure 5 is a flowchart from an application request to an SPM action. Ex. 1001, 3:6–8, 7:38–39. In step 502, an application is invoked, such as playing a movie. *Id.* at 7:40–41. In step 504, the application determines the required frequency for performance of an IP unit, for example, a specified frequency for an IP unit for an MPEG decoder. *Id.* at 7:41–44. In step 506, the application invokes PMCL 218 application program interface (API) call.

*Id.* at 7:50–51; *see also* 5:15–17 (explaining acronym). In step 508, PMCL 218 determines possible trade-offs available for the IP unit and selects a frequency rate, Vdd, and Vt that best meets the given requirements and, in step 510, determines the applicable SPMs 264 and 274. *Id.* at 7:60–64.<sup>3</sup> In step 512, PMCL 218 writes the selected settings for SPMs 264 and 274 to MPM 280, which converts the settings into commands (step 514) and sends them to SPMs 264 and 274 (step 518). *Id.* at 8:1–16, Fig. 5. In steps 522 to 528, SPM 264 performs the commanded actions by, e.g., switching a Vdd mux, switching a clock mux, or changing the Vt on the associated transistors. *Id.* at 8:21–27, Fig. 5.

Figure 8 of the '811 Patent is a flowchart from an application request to an SPU action. Ex. 1001, 3:13–15, 8:53–54. Steps 802 to 810 are similar to steps 502 to 510 of Figure 5. *Compare id.* at 7:40–64, Fig. 5 (steps 502 to 510), *with id.* at 8:55–9:5, Fig. 8 (steps 802 to 810).

#### C. Illustrative Claim

Of the challenged claims of the '811 patent, claims 1, 17, 24, 30, 45, and 61 are independent claims. Claim 1, reproduced below with bracketed annotations inserted, is illustrative.

1. [1Pre] A system comprising:

[1a] an integrated circuit;

[1b] a plurality of power islands of the integrated circuit having associated power consumptions, each of the power consumptions adapted to be independently controlled; and

[1c] a power manager to control the power consumptions;

<sup>&</sup>lt;sup>3</sup> "Vdd" refers to "dynamic voltage source" (Ex. 1001, 4:56–58), and Vt refers to threshold voltage (*id.* at 7:3–5).

[1d] at least one of the power islands adapted to have the power manager control its associated power consumption by a) the at least one of the power islands being configured to have one of plural threshold voltages of variable threshold transistors selected, and b) the system being configured to perform, during operation, an action on the at least one of the power islands, the action including changing a frequency of operation or changing a supply voltage.

Ex. 1001, 13:24–38. Independent claims 17, 24, 30, 45, and 61 are similar to claim 1, with some exceptions. Claim 24 is directed to a "processor implemented method," rather than a system. Claims 17, 30, and 61 do not recite threshold voltages of variable threshold transistors. Claim 17 recites an "internal regulator" that provides a "supply voltage." *Id.* at 14:21–22. Claims 30 and 61 each recite that a first power island communicates "synchronously and asynchronously" with a second power island. *Id.* at 15:20–22, 16:60–63.

D. Asserted Challenges and Evidence

Petitioner raises the following challenges to patentability.

| Claims Challenged                              | 35 U.S.C. § <sup>4</sup> | References/Basis                           |

|------------------------------------------------|--------------------------|--------------------------------------------|

| 1–11, 14–19, 21–26, 28–35, 38–55, 58–65, 68–74 | 103                      | Nowka, <sup>5</sup> Borkar <sup>6</sup>    |

| 12, 36, 56, 66                                 | 103                      | Nowka, Borkar,<br>Rincon-Mora <sup>7</sup> |

| 13, 20, 27, 37, 57, 67                         | 103                      | Nowka, Borkar, Iyengar <sup>8</sup>        |

| 1–11, 14–19, 21–26, 28–35, 38–55, 58–65, 68–74 | 103                      | Nicol, <sup>9</sup> Borkar                 |

| 12, 36, 56, 66                                 | 103                      | Nicol, Borkar,<br>Rincon-Mora              |

| 13, 20, 27, 37, 57, 67                         | 103                      | Nicol, Borkar, Iyengar                     |

Pet. 1–2. Petitioner submits the Declaration of Tajana Rosing, Ph.D. Ex. 1003.

<sup>6</sup> Ex. 1006, US 6,484,265 B2, issued November 19, 2002 ("Borkar"). Petitioner contends that Borkar is prior art under § 102(a)/(e). Pet. 2.

<sup>7</sup> Ex. 1007, US 6,188,211 B1, issued February 13, 2001 ("Rincon-Mora"). Petitioner contends that Rincon-Mora is prior art under § 102(b). Pet. 2.

<sup>8</sup> Ex. 1022, US 5,300,824, issued April 5, 1994 ("Iyengar"). Petitioner contends that Iyengar is prior art under § 102(b). Pet. 2.

<sup>9</sup> Ex. 1008, US 6,141,762, issued October 31, 2000 ("Nicol"). Petitioner contends that Nicol is prior art under § 102(b). Pet. 2.

<sup>&</sup>lt;sup>4</sup> The Leahy-Smith America Invents Act ("AIA"), Pub. L. No. 112–29, amended §§ 102 and 103 of Title 35, effective March 16, 2013. Because the filing date of the '811 Patent is before this date, we refer to the pre-AIA versions of §§ 102 and 103. Ex. 1001, code (22).

<sup>&</sup>lt;sup>5</sup> Ex. 1004, *A 32-bit PowerPC System-on-a-Chip With Support for Dynamic Voltage Scaling and Dynamic Frequency Scaling*, IEEE J. of Solid-State Circuits, Vol. 37, No. 11, November 2002 ("Nowka"). Petitioner contends that Nowka is prior art under § 102(a). Pet. 2.

#### III. ANALYSIS

#### A. Legal Standards

"In an [*inter partes* review], the petitioner has the burden from the onset to show with particularity why the patent it challenges is unpatentable." *Harmonic Inc. v. Avid Tech., Inc.*, 815 F.3d 1356, 1363 (Fed. Cir. 2016) (citing 35 U.S.C. § 312(a)(3) (requiring *inter partes* review petitions to identify "with particularity . . . the evidence that supports the grounds for the challenge to each claim")); *see also* 37 C.F.R. § 42.104(b) (requiring a petition for *inter partes* review to identify how the challenged claim is to be construed and where each element of the claim is found in the prior art patents or printed publications relied upon).

A patent claim is unpatentable under 35 U.S.C. § 103 if the differences between the claimed subject matter and the prior art are such that the subject matter, as a whole, would have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains. *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 406 (2007). The question of obviousness is resolved based on underlying factual determinations including: (1) the scope and content of the prior art; (2) any differences between the claimed subject matter and the prior art; (3) the level of ordinary skill in the art; and (4) when presented, objective evidence of obviousness or non-obviousness. *Graham v. John Deere Co.*, 383 U.S. 1, 17–18 (1966).

Additionally, the obviousness inquiry typically requires an analysis of "whether there was an apparent reason to combine the known elements in the fashion claimed by the patent at issue." *KSR*, 550 U.S. at 418 (citing *In re Kahn*, 441 F.3d 977, 988 (Fed. Cir. 2006) (requiring "articulated reasoning with some rational underpinning to support the legal conclusion of

obviousness")). Petitioner cannot satisfy its burden of proving obviousness by employing "mere conclusory statements," but "must instead articulate specific reasoning, based on evidence of record, to support the legal conclusion of obviousness." *In re Magnum Oil Tools Int'l, Ltd.*, 829 F.3d 1364, 1380 (Fed. Cir. 2016).

### B. Level of Ordinary Skill in the Art

At this stage of the proceeding, there is no dispute about the level of ordinary skill in the art. Based on the testimony of Petitioner's declarant, we determine that a person of ordinary skill in the art ("POSITA") would have had a bachelor of science degree in electrical engineering, computer engineering, computer science, or a related field, and two years of experience in the research, design, development, or testing of electronic circuits or components or software for controlling electronic circuits or components, or the equivalent, with additional education substituting for experience and vice versa. Ex. 1003  $\P$  21. We find that the level of ordinary skill in the art, as articulated above, is consistent with the level of technical understanding and competence reflected in the Specification of the '811 Patent and the asserted prior art references.

#### C. Claim Construction

In an *inter partes* review, we apply the same claim construction standard as would be used by a district court to construe a claim in a civil action involving the validity or infringement of a patent. 37 C.F.R. § 42.100(b). Under that standard, claim terms are given their ordinary and customary meaning, as would have been understood by a person of ordinary skill in the art at the time of the invention, in light of the language of the claims, the specification, and the prosecution history of record. *Id.*; *Phillips*

*v. AWH Corp.*, 415 F.3d 1303, 1312–19 (Fed. Cir. 2005) (en banc); *Thorner v. Sony Comput. Entm't Am. LLC*, 669 F.3d 1362, 1365–66 (Fed. Cir. 2012). "The Board is required to construe 'only those terms . . . that are in controversy, and only to the extent necessary to resolve the controversy."" *Realtime Data, LLC v. Iancu*, 912 F.3d 1368, 1375 (Fed. Cir. 2019) (quoting *Vivid Techs., Inc. v. Am. Sci. Eng'g, Inc.*, 200 F.3d 795, 803 (Fed. Cir. 1999)).

Petitioner states that, "[f]or purposes of this proceeding only, Petitioner submits that no claim terms require a formal construction for purposes of addressing the Grounds in this Petition," and impliedly contends that all claim terms have their ordinary and customary meaning. Pet. 5. Petitioner acknowledges that claim construction orders were issued in prior district court litigations involving the '811 Patent. *Id.* at 5–6 (citing Exs. 1011, 1012).<sup>10</sup> According to Petitioner, "the Board does not need to address any of the prior constructions to resolve the patentability disputes before the PTAB, and that none of the constructions impact the invalidity analysis in this Petition." *Id.* at 6.

Patent Owner also acknowledges that there are two claim construction orders from previous district court litigations. *See* Prelim. Resp. 17–18. Patent Owner asserts that, additionally, there currently is a claim construction dispute in the co-pending district court litigation concerning the meaning of a limitation that is pertinent to our determination as to whether to

<sup>&</sup>lt;sup>10</sup> Exhibit 1011 is an April 29, 2013, claim construction order in *Mosaid Technologies Inc. v. Freescale Semiconductor, Inc.*, No. 6:11-cv-00173 (E.D. Tex.). Exhibit 1012 is a January 9, 2015, claim construction order in *Conversant Intellectual Property Management Inc. v. Xilinx, Inc.*, No. 6:12-cv-00847 (E.D. Tex.). Petitioner informs us that these prior litigations were voluntarily dismissed based on settlement. Pet. 5–6, 100.

institute an *inter partes* review, specifically referring to "'a plurality of power islands,' each power island with a power consumption either adapted to be (or being) 'independently controlled' . . . 'or being 'independently controllable.'" Prelim. Resp. 17–18. Patent Owner further argues that, in light of the known dispute, Petitioner should have explicitly proposed a construction rather than asserting that no construction is necessary. *See id.* at 17–23. Patent Owner's argument is addressed below in the context of the Nowka-based grounds.

### D. Petitioner's Nowka-based Challenges

Petitioner contends that claims 1–74 are unpatentable as obvious based on Nowka and Borkar, by themselves or in further combination with Rincon-Mora or Iyengar. Pet. 6–55. Patent Owner opposes. Prelim. Resp. 1–32. We begin with overviews of Nowka and Borkar.

# 1. Nowka (Ex. 1004)

Nowka is journal article titled, "A 32-bit PowerPC System-on-a-Chip With Support for Dynamic Voltage Scaling and Dynamic Frequency Scaling." Ex. 1004, 1441.<sup>11</sup> Nowka describes a system-on-a-chip (SOC) processor that uses "dynamic voltage scaling and on-the-fly frequency scaling to adapt to the dynamically changing performance demands and power consumption constraints of high-content, battery powered applications." *Id.* (Abstract, Introduction).

Under the heading, "System Overview," Nowka asserts that the SOC "makes use of active power reduction techniques to dynamically match the power consumption with the requirements of the application." Ex. 1004,

<sup>&</sup>lt;sup>11</sup> We refer to the original page numbers of Nowka, not those added by Petitioner.

1442 (lefthand column). According to Nowka, "[t]he active power consumption is reduced when resource[] demands are low through the use of dynamic voltage scaling, dynamic frequency scaling, unit and register level functional clock gating." *Id*.

Under the heading, "Dynamic Voltage Scaling," Nowka states, "[t]he primary means of matching the performance and power consumption of this device to the application is through the use of dynamic voltage scaling (DVS)," which "adjust[s] the supply voltage dynamically to meet the performance demands while minimizing power consumption." Ex. 1004, 1442 (righthand column).

Under the subheading, "Dynamic Voltage Scaling Architecture," Nowka discloses, "[t]o support DVS in this SOC, the power distribution has been divided into four distinct domains," consisting of "two persistent voltage domains, one dynamically voltage-scaled logic domain and one internally derived domain." Ex. 1004, 1442 (righthand column). The four domains are shown in Figure 3, which identifies an "SOC Logic DVS Supply Domain," a "Regulated 1.0V PLL Supply Domain," a "Persistent 3.3V I/O Supply Domain," and a "Persistent 1.8V Battery-Backed Domain." *Id.* at 1443, Fig. 3.

Under the heading, "Scalable Clocking Subsystem," Nowka discloses that "on-the-fly frequency modification techniques can be used to provide dynamic frequency scaling for additional active power reduction." Ex. 1004, 1444 (righthand column). According to Nowka, "[w]hen the performance demands of the application decrease, the system software can lower the operating frequency." *Id.* Nowka discloses that, "[u]nder software control, at a given supply voltage, the frequency of the core can be varied from the maximum frequency down to 1/64th of the maximum." *Id.*

Nowka discusses Figure 8 under the heading, "Dynamic Voltage and Frequency Scaling Measurements." Ex. 1004, 1444 (righthand column). Figure 8 shows voltage versus time traces for the total SOC power, the SOC logic power, the SOC I/O power, and the SOC logic supply voltage (Vdd). *Id.* at 1444–45 (righthand column, Fig. 8). Figure 8 shows how power is affected by changes in frequency<sup>12</sup> and logic supply voltage under control of the clock and power management software. *Id*.

Under the heading, "Active Power Management," Nowka states that dynamic voltage scaling and dynamic frequency scaling are used to reduce the power consumption of the processor and control power consumption "on a very fine time scale." Ex. 1004, 1445 (lefthand column). According to Nowka, "[t]hrough voltage and frequency scaling and clock gating, the performance/watt of this design can be varied by more than a factor of four." *Id.* (righthand column).

Under the heading "Standby Power Management," Nowka discloses that "[s]everal modes of standby operation are employed to achieve a range of standby power levels." Ex. 1004, 1446 (lefthand column). According to Nowka, "[t]he on-chip clock and power supervisor, in response to software commands and timeout and interrupt events, manages the clocks, internal state and external power supply to control the standby power." *Id*.

By way of summary, Nowka states, "[u]nder software control, both the voltage and the frequency of the processor can be modified, thereby allowing the performance demands of the application to be met while

<sup>&</sup>lt;sup>12</sup> According to Nowka, the clock and power management adjusts the frequency by modifying the output clock divider of the phase locked loop (PLL). Ex. 1004, 1444 (righthand column under the heading "Scalable Clocking Subsystem").

minimizing the dynamic power consumption." Ex. 1004, 1446 (righthand column). According to Nowka, "[b]y applying these techniques," high frequencies and low power consumption can be achieved, "thereby dynamically adapting to the changing needs for performance and power demanded by the applications." *Id*.

#### 2. Borkar (Ex. 1006)

Borkar relates to integrated circuits (also called chips) and discloses using control circuitry and software to control transistor body bias, supply voltage, and clock frequency to control chip parameters, including performance, power consumption, and temperature. Ex. 1006, code (57), 1:8–18. Borkar explains that "[b]ody bias refers to the relationship between voltage of the source (Vsource) of a field effect transistor (FET transistor) and voltage of the body (Vbb) of the FET transistor." *Id.* at 3:34–36. Borkar further explains that the threshold voltage (Vt) of a transistor depends on the relationship between Vbb and Vsource. *Id.* at 3:46–49.

Borkar discloses control circuitry for changing the body bias, supply voltage, and/or clock signal settings to control parameters of the processor, including temperature and power consumption. Ex. 1006, 2:61–3:2, 4:3–5, 4:12–32 (responses to changes in temperature), 4:57–5:10 (power considerations), Figs. 1, 2 (voltage and frequency control circuitry 118, 144). In this context, Borkar discloses:

In some embodiments, when the battery level signal is below a certain level, the supply voltage is lowered, the frequency of a processor clock is lowered, and/or the bias signals are changed to raise the threshold voltages of some or all of the transistors. This will reduce the power consumption to maintain the battery.

*Id.* at 5:25–30. Borkar states there are "tradeoffs" between processor performance and power consumption and "a high processor performance can

be achieved" by "providing proper settings with each of supply voltage, clock frequency, and threshold voltages." *Id.* at 6:15–23.

Borkar discloses that determination of the body bias, supply voltage, and/or clock settings "may occur by circuitry in [the] peripheral interface . . . in response to software control of [the] operating system . . . and/or a program, rather than in hardware as in control circuitry." Ex. 1006, 7:51–65, Figs. 3, 4. According to Borkar, the control circuitry and peripheral interface (Figs. 1–4) are "not restricted to [a] single chip" and "may also be used to control the settings for more than one chip (e.g., multiple processors)." *Id.* at 9:20–24.

Borkar also discloses "circuitry to detect mismatches of transistor parameters in different groups of transistors and to correct the mismatches by providing different signals levels to the different groups of transistors." Ex. 1006, 9:65–10:2. Borkar explains that the fabrication process may result in transistor parameter variations between two groups of transistors or domains, "[f]or example, a first domain as a whole may perform differently than a second domain as a whole." *Id.* at 9:25–31, 9:48–55. Borkar's Figures 5 and 7 show domains 234 and 238 and control circuitry 262, which is used to reduce mismatch by providing a clock signal, a body bias signal, and a supply voltage signal to each domain. *Id.* at 11:22–27, 11:40–43, 11:55–58, 13:8–11, Figs. 5, 7. According to Borkar, the goals of detecting and reducing mismatch include "keeping power consumption below a particular level, keeping temperature in a particular range, obtaining the highest possible performance, and obtaining the highest performance while not exceeding a particular power consumption level." *Id.* at 12:10–15.

# 3. Discussion

Limitation 1b recites, "a plurality of power islands of the integrated circuit having associated power consumptions, each of the power consumptions adapted to be independently controlled." Ex. 1001, 13:26–28.

This limitation contains two phrases. As to the first, Petitioner maintains that "[t]he '811 patent defines 'power island' as 'any section, delineation, partition, or division of the integrated circuit [] where power consumption is controlled within the section, delineation, partition, or division." Pet. 59 (quoting Ex. 1001, 3:59–62) (alteration in original); *see also id.* at 16 (applying this definition to Nowka). The second phrase in the limitation pertains to how the power consumption is controlled, specifically reciting that it is "adapted to be independently controlled."<sup>13</sup>

Petitioner offers two alternative contentions as to how the Nowka-Borkar combination purportedly renders obvious subject matter having this limitation. *See* Pet. 15–19.

Petitioner first contends that Nowka discloses the limitation. Id.

at 15–16. Specifically, Petitioner contends that:

Nowka discloses multiple power domains on the IC, namely the "four distinct domains" supplied different voltages, depicted in Figure 3. MTK-1004, 1442. Domain 1 is powered by a *persistent* 3.3V supply; domain 2 is powered by a *persistent*, battery-backed 1.8V supply; domain 3 receives a *dynamic* supply varied between 1.0–1.8V which is controlled by external DC/DC converter; domain 4 is powered by an on-chip linear regulator and receives a *constant* 1V supply from the dynamically-varying logic supply. MTK-1004, 1442.

<sup>&</sup>lt;sup>13</sup> Limitation 1d further requires the power consumption of at least one power island to be adapted to be controlled based on two specified parameters—selection of a threshold voltage of a variable threshold transistor and either changing frequency or changing voltage.

*Id.* (emphasis added). Thus, Petitioner is relying on one dynamic voltage supply, two persistent voltage supplies, and one constant voltage supply.

For the first phrase of limitation 1b, Petitioner is mapping Nowka's domains to the recited "plurality of power islands." *See id.* at 16 (using the words of the Specification's definition). For the second phrase, Petitioner contends that "[t]hese domains . . . have power consumptions adapted to be independently controlled because they receive separate voltage supplies which can be independently controlled." *Id.* at 16 (citing Ex. 1004, 1442; Ex. 1003 ¶ 63).

Patent Owner argues that the disclosures relied on by Petitioner "expressly show that three of Nowka's four 'domains' are supplied with *constant* voltages, not variable voltages, and certainly not independently variable voltages," and that "[t]his material provides no support whatsoever for Petitioner's expert's assertion that the voltages supplied to these domains 'can be independently controlled.'" Prelim. Resp. 26 (citing Ex. 1003 ¶ 63); *see id.* (Patent Owner arguing that "Petitioner's expert's conclusory statements . . . are entitled to little weight."). We understand Patent Owner to argue that the disclosure of "a section of circuitry [that] receives a 'separate voltage supply'" is not a disclosure of having the capability of independently controlling power consumption within that section of circuitry, within the meaning of the '811 patent. *See id.* at 25–26.

Patent Owner also argues that Petitioner has failed to satisfy its "burden to construe the claim and demonstrate that the construed claims are satisfied." Prelim. Resp. 20 (citing 37 C.F.R. §§ 42.104(b)(3)–(4)). Patent Owner asserts that claim construction is a disputed issue in the co-pending district court litigation, and argues that the parties have agreed in the district court that power consumption being independently controlled means

independently varying one or more power characteristics. *See id.* at 19; *see also id.* at 17–18 (indicating that the dispute in the district courts pertains to whether it is both operating voltage and frequency of operation that are varied or it need be only one of those parameters). Patent Owner argues that Petitioner's position in this *inter partes* review is inconsistent with the position it has taken in the district court. *See, e.g., id.* at 20 ("Petitioner cannot—and does not even attempt to—argue that the cited art teaches 'a plurality of power islands' by comparing the art to either party's (or either district court's) construction.").

The dispute here requires a determination of the meaning of "adapted to be independently controlled." This was a foreseeable issue. Neither party, however, provides us with an adequate claim construction analysis from which to make that determination. As Patent Owner notes, Petitioner bears a burden in this regard—a petition must set forth "[h]ow the challenged claim is to be construed" and "[h]ow the construed claim is unpatentable [under the petitioner's ground]." 37 C.F.R. § 42.104(b)(3)–(4).

We understand Petitioner to contend that Nowka's disclosure of separately supplied constant/persistent voltages reads on the recitation "adapted to be independently controlled." *See* Pet. 16 ("These domains further have power consumptions adapted to be independently controlled because they receive separate voltage supplies which can be independently controlled."). However, Petitioner's contention is conclusory and does not adequately or persuasively explain why a person of ordinary skill in the art reading the claim in light of the Specification would have that understanding. *See id.* at 15–16. Petitioner describes the '811 patent as indicating that a problem in the prior art was that "the voltages in the power island and the frequencies of the multiple clocks are static; [t]he voltages

and frequencies do not dynamically change based on the needs and operation of the integrated circuit." *Id.* at 3 (quoting Ex. 1001, 2:21–27) (alteration in original; internal quotations omitted). Petitioner characterizes the '811 patent as proposing, as a purported solution to the prior art's problem, "managing the power consumption of an integrated circuit ('IC') using power islands whose power consumption is independently controlled." *Id.* (citing Ex. 1001, code (57) (Abstract), 2:31–34; Ex. 1003 ¶ 37). Petitioner does not explain adequately why, in light of that, a person of ordinary skill in the art would understand Nowka's persistent or constant voltage domains, whose voltages are not dynamically changed, satisfy the limitation directed to power islands whose power consumption is independently controlled.

The paragraph of Dr. Rosing's declaration cited by Petitioner as support for its contention that all of Nowka's domains are power islands is worded a little differently than Petitioner' arguments. Ex. 1003 ¶ 63 (citied at Pet. 16). Dr. Rosing opines that "*Nowka's voltage domains satisfy the '811 patent's definition* of 'power island,' as each domain is a section, delineation, partition, or division of Nowka's SOC, and *each domain receives a different power supply*," and opines that receiving separate voltage supplies means that a domain can be independently controlled. *Id.* (emphasis added). This testimony is conclusory and—to the extent that it is an assertion that the '811 patent describes "independently controlled" as encompassing the act of merely providing a separate power supply, even if that supply is not a dynamically controllable and variable power supply lacks citation to intrinsic evidence support.

The Board declines to conduct, in the first instance, a full and proper analysis of the intrinsic and extrinsic evidence to determine whether Petitioner's application of Nowka's teachings to the recitation of "power

consumptions adapted to be independently controlled" is based on a proper claim construction.<sup>14</sup>

On the current record and in light of the specific factual circumstances here, we determine that Petitioner has not adequately shown, for purposes of institution, that Nowka teaches limitation 1b. As such, Petitioner has not demonstrated a likelihood of prevailing on its Nowka-based challenge to independent claim 1 under Petitioner's first alternative contention.

For its second alternative contention, Petitioner asserts that, if Nowka does not teach limitation 1b, "Borkar discloses and renders obvious this limitation." Pet. 17. Patent Owner argues that, "[a]lthough Petitioner's arguments are phrased in terms of what an alleged 'Nowka-Borkar combination' renders obvious, . . . Petitioner never specifies exactly how Nowka and Borkar are to be combined to arrive at this limitation." Prelim. Resp. 30–31 (citing Pet. 15). We find Patent Owner's argument to be persuasive.

Petitioner discusses Borkar's disclosures and concludes with the assertion that "a POSITA would have understood and found obvious that Borkar's domains are a plurality of power islands, each with a power consumption adapted to be independently controlled." Pet. 19 (citing Ex. 1003  $\P$  65). Thus, Petitioner's alternative position is that, if Nowka does not teach limitation 1b, then Borkar teaches it. However, Petitioner's analysis of limitation 1b ends there and does not explain adequately how the

<sup>&</sup>lt;sup>14</sup> In light of the determination here, the Board does not reach the issue of the proper construction of "a plurality of power islands . . . [with] power consumptions adapted to be independently controlled," and, specifically, does not decide whether being adapted to be independently controlled requires more than separate voltage supplies or requires dynamically changing parameters.

two references' separate teachings are proposed to be combined, and Petitioner has not explained adequately why a person of ordinary skill in the art would have made the unidentified combination. *See id.* at 17–19.

Under the heading, "The Nowka-Borkar Combination," Petitioner asserts that a person of ordinary skill in the art would have been motivated to combine Nowka's SOC and power management mechanism with Borkar's threshold voltage-tuning solution, Pet. 13, but does not assert that a POSITA would have combined Nowka with Borkar's first and second domains (asserted power islands, *id.* at 17–19). We understand that Petitioner's proposed combination relates to limitation 1d, not limitation 1b. *See id.* at 22 (addressing limitation 1d and cross-referencing the section of Petition that addresses motivation to combine). Although Petitioner contends that Borkar teaches limitation 1b, Petitioner does not explain how or why a POSITA would have combined that teaching with Nowka. *Id.* at 17–19.

We determine that Petitioner has not demonstrated a likelihood of prevailing on its Nowka-based challenge to independent claim 1 under Petitioner's second alternative contention.

Petitioner's contentions regarding the similar recitations in the remaining challenged independent claims are substantively the same. *See* Pet. 39–43, 45–47. Each of the remaining claims challenged in the Nowkabased grounds depends from one of these independent claims. Accordingly, having considered the parties' arguments and evidence, the Board determines that Petitioner has not demonstrated a reasonable likelihood of prevailing in its Nowka-based challenges to claims 1–74 (Grounds 1A–1C).

# E. Petitioner's Nicol-based Challenges

Petitioner contends that claims 1–74 are unpatentable as obvious based on Nicol and Borkar, by themselves, or in further combination with Rincon-Mora or Iyengar. Pet. 55–96. Patent Owner opposes. Prelim. Resp. 33–47.

# 1. Nicol (Ex. 1008)

Nicol pertains to "to electronic circuits and, more particularly to power consumption within electronic circuits." Ex.1008, 1:6–7. According to Nicol:

Improved operation of multi-processor chips is achieved by dynamically controlling processing load of chips and controlling, significantly greater than on/off granularity, the operating voltages of those chips so as to minimize overall power consumption. A controller in a multi-processor chip allocates tasks to the individual processors to equalize processing load among the chips, then the controller lowers the clock frequency on the chip to as low a level as possible while assuring proper operation, and finally reduces the supply voltage. Further improvement is possible by controlling the supply voltage of individual processing elements within the multi-processor chip, as well as controlling the supply voltage of other elements in the system within which the multiprocessor chip operates.

Id., code (57) (Abstract).

# 2. Discussion

Patent Owner asserts that "Petitioner argues that a POSITA would combine Nicol with Borkar but fails to sufficiently describe the combination," and that "Petitioner attempts to state its combination on pages 56-58 of the Petition . . . however, Petitioner never clearly articulates *what* its combination is." Prelim. Resp. 33. We agree with Patent Owner.

For each of the elements of independent claim 1, Petitioner contends that both references teach the element. *See* Pet. 58–65; *see, e.g., id.* at 59–62 (Petitioner contending that Nicol teaches limitation 1b, and then further contending that, "[t]o the extent it is argued that Nicol does not explicitly disclose a plurality of power islands, Borkar also discloses and renders obvious [the subject matter of limitation 1b]."). For most of the elements of claim 1, Petitioner's analysis ends there, without stating which reference's teaching is used in the combination and not clearly identifying the proposed combination. *See id.* at 58–65.

For limitation 1d, Petitioner first contends that Nicol discusses techniques concerning tuning the threshold voltages, "*which would motivate* a POSITA to implement selecting one of plural threshold voltages, either in light of Nicol alone, or in view of Borkar *as explained below.*" *Id.* at 64–65 (emphasis added). Petitioner then asserts that Borkar contains certain disclosures and concludes that paragraph with the assertion that "[a] POSITA *would have been motivated to combine Nicol and Borkar for the reasons previously explained.*" *Id.* at 65 (citing Section III.D.3 of the Petition; Ex. 1003 ¶ 210) (emphasis added). The cross-referenced Section III.D.3 contains contentions that the two references are similar. *Id.* at 56–57; *see, e.g., id.* at 57 ("Nicol and Borkar address the same known problem" and "[b]oth Nicol and Borkar also suggest the solution of dynamically controlling variables."). Petitioner further contends that:

The similarities across Nicol and Borkar's disclosures would have led a POSITA to incorporate Borkar's teachings in Nicol's dynamic power management. For example, Nicol discusses the need to adjust to temperature variations "to achieve high performance at varying operating temperatures and process corners." MTK-1008, 1:41-44, 1:65-67. A POSITA would have understood that the discussion of

temperature variation is closely related to the need to monitor power consumption because, as Borkar teaches, "performance, power consumption, and temperature are typically related." MTK-1006, 1:19-20; MTK-1003, ¶199. A POSITA would have understood that Borkar's power consumption monitoring mechanism would provide an additional check on the adverse effects of high power consumption (which causes high temperature) that Nicol discusses. MTK-1003, ¶199.

*Id.* at 57–58. We agree with Patent Owner's argument (Prelim. Resp. 34) that Petitioner's assertion that the similarities "would have led a POSITA to incorporate Borkar's teachings in Nicol's dynamic power management" is ambiguous as to what teachings are being proposed to be incorporated into Nicol's system. Also, we fail to see how Petitioner's more specific example of "Borkar's power consumption monitoring mechanism" constitutes an explanation as to how Nicol and Borkar are proposed to be combined for the aspect of limitation 1d involving controlling power consumption by selecting one of the "threshold voltages," or why a person of ordinary skill in the art would have been motivated by the disclosure of a monitoring mechanism to make the unexplained combination.

Petitioner has not demonstrated a likelihood of prevailing on its Nicol-based challenge to independent claim 1. Petitioner's contentions regarding the remaining challenged independent claims are similar. *See* Pet. 81–89. Each of the remaining claims challenged in the Nicol-based grounds depends from one of these independent claims. Accordingly, having considered the parties' arguments and evidence, the Board determines that Petitioner has not demonstrated a reasonable likelihood of prevailing in its Nicol-based challenges to claims 1–74 (Grounds 2A–2C).

# IV. ORDER

It is

ORDERED that the Petition is *denied* and no trial is instituted.

#### UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

MEDIATEK, INC., Petitioner,

v.

MOSAID TECHNOLOGIES INC., Patent Owner.

> IPR2024-00718 Patent 7,996,811 B2

HORVATH, Administrative Patent Judge, concurring.

#### CONCURRING OPINION

I concur with the Decision above, and write separately to explain why I agree to deny the Petition based on the Nowka-Borkar and Nicol-Borkar challenges.

#### A. The Nowka-Borkar challenge

The Decision above finds Petitioner fails to sufficiently demonstrate that the Nowka-Borkar combination teaches "a plurality of islands of the integrated circuit having associated power consumptions, each of the power consumptions adapted to be independently controlled." Dec. 17–25 (the "power islands" limitation). I agree that Nowka does not teach the limitation

and Petitioner has not asserted, let alone sufficiently explained, how or why a person skilled in the art would have modified Nowka to include Borkar's first and second domains (power islands) so that the combination teaches the limitation. *Id.* However, I disagree to the extent the Decision faults Petitioner for failing to provide a claim construction analysis that supports its interpretation of Nowka's disclosures. Claim construction is a question of law for the Board to decide. *See Markman v. Westview Insts., Inc.*, 517 U.S. 370, 391 (1996) ("we hold the interpretation of the [claim term] in this case is an issue for the judge").

The '811 patent defines a power island as "any section, delineation, partition, or division of the integrated circuit 110, where power consumption is controlled within the section, delineation, partition, or division." Ex. 1001, 3:59–62. Key to this definition is that "power consumption is *controlled within* the section," i.e., within the power island. *Id.* (emphasis added). This is shown in every embodiment in the patent. Figure 1 illustrates that each of power islands 112–118 can have their power consumptions controlled by power manager 120. *Id.*, Fig. 1. Power manager 120 is:

any circuitry, device, or system configured to (1) determine a target power level for one of the power islands 112, 114, 116, and 118 where power consumption is independently controlled within each of the power islands 112, 114, 116, and 118, (2) determine action to change a consumption power level of the one of the power islands . . . to the target power level, and (3) perform the action to change the consumption power level of the one of the power islands . . . to the target power level of the one of the power islands . . . to the target power level.

*Id.* at 4:25–34. Although the power manager need only control power consumption in *one* of the power islands, each of the power islands is controllable by the power manager because each contains power control

circuitry. See id. at 4:11–14 ("each of the power islands 112, 114, 116, and 118 includes power control circuitry. Power control circuitry is any circuitry configured to *control power within* one of the power islands.") (emphasis added). Thus, each of power islands 112-118 has a variable and *controllable* power consumption, i.e., one that can be *changed* to a target power level. Figure 2, similarly, illustrates that each of power islands 260 and 270 has a variable power consumption that can be changed by master power manager ("MPM") 280. Id., 5:54–56 ("the MPM communicates with existing IPMs [intermediate power managers] and SPMs [slave power managers]... to control power within the power islands 260 and 270"), Fig. 2. Figure 4 illustrates power island 270 includes both (1) low power memory block 272 having sleep power down circuitry 450 and (2) SPM 274 to control the sleep power down circuitry. Id. at 7:12–17, Fig. 4. Figure 10, like the other Figures in the patent, illustrates each of a plurality of power islands in SOC 1000 has a variable power consumption that can be controlled by MPM 1070. Id. at 10:15-21 ("The CPU 1010, the local memory 1020, the memory controller 1030, the mixed signal circuitry 1040, the application specific circuitry 1050, the PCI-X circuitry 1060, the Ethernet circuitry 1080, and the USB circuitry 1090 are all *power islands in* which power is controlled within the power islands by power managers.") (emphasis added), Fig. 10.

In short, every power island disclosed in the patent is a section of an integrated circuit whose power consumption can be changed by a power manager, i.e., whose power consumption is variable. This narrow disclosure informs the meaning of the patent's definition of the term "power island." *See Gentry Gallery, Inc. v. Berkline Corp.*, 134 F.3d 1473, 1480 (Fed. Cir. 1998) ("claims may be no broader than the supporting disclosure, and

therefore a narrow disclosure will limit claim breadth"); *see also Ruckus Wireless, Inc. v. Innovative Wireless Sol's, LLC*, 824 F.3d 999, 1004 (2016) (limiting the term "communication path" to a wired communication path because "the specification makes no mention of wireless communications").

Here, the patent's definition of "power island," i.e., an IC section "where power consumption is controlled within the section," is limited by the patent's narrow disclosure to mean an IC section having a variable power consumption. Petitioner fails to demonstrate how any of Nowka's persistent 3.3V I/O supply, persistent 1.8V battery-backed, or regulated (i.e., constant) 1.0V PLL supply domains have a variable power consumption and, therefore, read on the patent's definition of a power island.

#### B. The Nicol-Borkar challenges

Petitioner contends that both Nicol and Borkar separately teach each of the elements of independent claim 1. *See* Decision ("Dec.") 24; Pet. 58– 65. I agree that Petition's challenge based on a *combination* of Nicol and Borkar fails for the reasons stated in the Decision. Dec. 25. However, because Petitioner argues Nicol and Borkar separately teach all the limitations of claim 1, our analysis should not end there. *See Cohesive Techs. V. Waters Corp.*, 543 F.3d 1351, 1364 (Fed. Cir. 2008) ("[P]rior art references that anticipate a claim will usually render that claim obvious. . . ."); *Realtime Data, LLC v. Iancu*, 912 F.3d 1368, 1373 (Fed. Cir. 2019) (the Board "did not err when it concluded that claim 1 was invalid under § 103 based on [a single reference]" and was "free to come to the very conclusion it reached: that [because the reference] disclosed every element of [the] claims" and "because the Board did not rely on [a secondary

reference] for the disclosure of a particular element or teaching, the Board had no obligation to find a motivation to combine [the two references].")

Petitioner sufficiently demonstrates that Borkar alone discloses all the limitations of independent claims 1, 17, and 24. See Pet. 58-65. However, Petitioner does not rely on Borkar for teaching the limitations recited in some of their dependent claims. See, e.g., Pet. 69, 78, 82 (failing to identify any disclosure in Borkar to teach the limitations recited in claims 5, 11, 19, and 21). Additionally, for claims 31–74, Petitioner fails to demonstrate how Borkar teaches the limitation, expressly recited in claims 30 and 61, of "a first of the power islands being configured to *communicate synchronously* and asynchronously with a second of the power islands." Ex. 1001, 15:19-22, 16:60–63 (emphasis added). Petitioner argues this limitation is met by Borkar's disclosure that some "groups of transistors," which Petitioner identifies as power islands, "may run off the same clock signal or otherwise need to run synchronously" and there may be other "groups of transistors that run off a different clock signal or that are asynchronous." Pet. 85 (quoting Ex. 1006, 10:6–7, 10:16–18). But this merely indicates that different "groups of transistors" may run synchronously or asynchronously. It does not indicate that a first group of transistors (first power island) even communicates with a second group of transistors (second power island), let alone that the first group communicates synchronously *and* asynchronously with the second group. See Pet. 60–62, Figs. 6–7 (Petitioner identifying a first group of transistors as a first power island and a second group of transistors as a second power island). Accordingly, Petitioner demonstrates a reasonable likelihood of showing about one third of the challenged claims are unpatentable as obvious over the Nicol-Borkar combination due to the disclosures in Borkar alone.

Petitioner likewise sufficiently demonstrates that Nicol alone discloses all the limitations of independent claims 1, 17, and 24. See Pet. 58–65. However, Petitioner does not rely on Nicol for teaching all of the limitations recited in some of their dependent claims. See, e.g., Pet. 70-78, 82, 83 (relying on Borkar to teach at least some of the limitations recited in claims 6-10, 14, 16, 23, 25, 26, 28, 29). Additionally, for claims 31-74, Petitioner fails to demonstrate how Nicol teaches the limitation, expressly recited in claims 30 and 61, of "a first of the power islands being configured to communicate synchronously and asynchronously with a second of the power islands." Ex. 1001, 15:19–22, 16:60–63 (emphasis added). Petitioner argues this limitation is met by Nicol's disclosure of "asynchronous communication between its Pes, which can operate at different frequencies." Pet. 84 (citing Ex. 1008, 6:14–21, 6:29–33, Fig. 4). But this discloses only discloses only asynchronous communication between power islands and the claim expressly requires both synchronous and asynchronous communication. Accordingly, Petitioner demonstrates a reasonable likelihood of showing about one-sixth of the challenged claims are unpatentable as obvious over the Nicol-Borkar combination due to the disclosures in Nicol alone.

In sum, for the reasons discussed above, Petitioner demonstrates a reasonable likelihood of showing only about one-third of the challenged claims are unpatentable over the Nicol-Borkar combination. Moreover, for the reasons discussed in the Decision, Petitioner fails to demonstrate that any of 74 claims challenged over the Nowka-Borkar combination are unpatentable. Thus, at best, Petitioner demonstrates a likelihood of succeeding on only about one-sixth of its challenges. On these facts, denial of institution is appropriate. *See* Patent and Trial Appeal Board

Consolidated Trial Practice Guide November 2019, 64 ("If a panel determines that a petition meets the standards for institution in relation to fewer than all the challenges presented . . . the panel will evaluate all the challenges and determine whether, in the interests of efficient administration of the Office and integrity of the patent system, the entire petition should be denied.").

#### UNITED STATES PATENT AND TRADEMARK OFFICE

# BEFORE THE PATENT TRIAL AND APPEAL BOARD

MEDIATEK, INC., Petitioner,

v.

MOSAID TECHNOLOGIES INC., Patent Owner.

> IPR2024-00718 Patent 7,996,811 B2

ROESEL, Administrative Patent Judge, dissenting.

I respectfully dissent from the decision denying institution. In my view, Petitioner's challenge to at least independent claim 1 based on Nowka and Borkar meets the reasonable likelihood standard. On that basis, I would institute an *inter partes* review.<sup>15</sup>

<sup>&</sup>lt;sup>15</sup> I agree that Petitioner's challenge based on Nicol and Borkar does not meet the reasonable likelihood standard for the reasons set forth in the Decision of the Board.

### 1. Limitation [1b]—Nowka

Claim element [1b] recites "a plurality of power islands of the integrated circuit having associated power consumptions, each of the power consumptions adapted to be independently controlled." Ex. 1001, 13:26–28.

Petitioner contends that Nowka's "four distinct domains" are power islands "because they are each a 'section, delineation, partition, or division' on the SOC where 'power consumption is controlled within the section, delineation, partition, or division." Pet. 16 (citing Ex. 1001, 3:59–62). Petitioner further contends that Nowka's domains "have power consumptions adapted to be independently controlled because they receive separate voltage supplies which can be independently controlled." *Id.* (citing Ex. 1004, 1442, Fig. 3).

According to the Decision of the Board, the Petition is deficient for not construing the phrase, "adapted to be independently controlled," and not adequately explaining its contention that Nowka's four domains "have power consumptions adapted to be independently controlled because they receive separate voltage supplies which can be independently controlled." Maj. 19–21 (citing Pet. 16).<sup>16</sup> I disagree.

In my view, there was no need for Petitioner to construe the phrase, "adapted to be independently controlled," and Petitioner's contention is adequate to support institution. Petitioner and Dr. Rosing make their position clear. Pet. 16 (citing Ex. 1003 ¶ 63; Ex. 1004, 1442). Nowka's four domains have power consumptions that are each "adapted to be independently controlled" because each receives a separate voltage that can

<sup>&</sup>lt;sup>16</sup> I cite the Decision of the Board as "Maj." I cite the concurring opinion as "Con."

be independently controlled. There is no dispute (and my colleagues agree) that controlling voltage is one way to control power consumption. In fact, claim 1 itself identifies supply voltage as one way of controlling power consumption. Ex. 1001, 13:36–38 (limitation [1d], clause b)).

Significantly, Patent Owner does not argue that Petitioner needed to construe the phrase, "adapted to be independently controlled" and does not contest the adequacy of Petitioner's contention for this phrase. Instead, Patent Owner relies on a construction for "power islands" that neither of my colleagues adopts. Patent Owner argues that a "power island" is "a section of an integrated circuit where power consumption is controlled by 'independently varying' one or more power characteristics, including at least one of an 'operating voltage' or a 'frequency of operation.'" Prelim. Resp. 19 (quoting Exs. 1011, 1012); *see also id.* at 25–26 (relying on this construction to distinguish Nowka). Patent Owner argues that "three of Nowka's four 'domains' are supplied with *constant voltages, not variable voltages*, and certainly not *independently variable voltages*." *Id.* at 26 (emphasis added).

In my view, the term "power islands" should be construed consistent with the express definition in the '811 Patent. *Sinorgchem Co., Shandong v. Int'l Trade Comm'n*, 511 F.3d 1132, 1138 (Fed. Cir. 2007) ("A definition set forth in the specification governs the meaning of the claims."). The correct construction is "any section, delineation, partition, or division of the integrated circuit within which power consumption is controlled." Ex. 1001, 3:59–62 (similar wording). That is the construction applied by Petitioner. Pet. 16 (citing Ex. 1001, 3:59–62). The correct construction for "power islands" does not require a variable voltage or an independently variable voltage, as argued by Patent Owner. Prelim. Resp. 26.

Patent Owner additionally argues that Nowka "provides no support whatsoever for Petitioner's expert's assertion that the voltages supplied to these domains 'can be independently controlled.'" Prelim. Resp. 16. That argument similarly relies on an incorrect claim construction. There is no requirement that *voltage* can be independently controlled in each of the power islands. Claim 1 says "each of the power consumptions adapted to be independently controlled," but requires only "at least one of the power islands" be capable of having its supply voltage changed. Ex. 13:34–38 (limitation [1d]). There is no dispute (and my colleagues agree) that Nowka discloses at least one power island—the logic domain—whose power consumption is controlled by changing the voltage.

The Decision of the Board faults Petitioner for not adequately explaining why "a person of ordinary skill in the art would understand Nowka's persistent or constant voltage domains, whose voltages are not dynamically changed, satisfy the limitation directed to power islands whose power consumption being is independently controlled." Maj. 20. This determination improperly reads a limitation into the claim. The '811 Patent states that "one problem" with prior integrated circuits that employ voltage islands or multiple clocks to lower power consumption is that "the voltages" in the power island and the frequencies of the multiple clocks are static" and "do not dynamically change based on the needs and operation of the integrated circuit." Ex. 1001, 2:21–27. The '811 Patent addresses this problem by providing power managers for an integrated circuit. Ex. 1001, code (57), 2:31–34. Nothing in the Specification or the claims supports the Board's interpretation of the phrase, "adapted to be independently controlled," as excluding a power island having a persistent or constant voltage. Claim 1 makes clear that power consumption can be controlled by

"changing a frequency of operation *or* changing a supply voltage." *Id.* at 13:34–38 (limitation [1d]; emphasis added). Claim 1 does not require that each power island have a voltage capable of being dynamically changed.

The concurring opinion states, "the ['811] patent's definition of 'power island,' i.e., an IC section 'where power consumption is controlled within the section,' is limited by the patent's narrow disclosure to mean an IC section having a *variable power consumption*." Con. 4 (emphasis added). I disagree. The concurrence is improperly reading a "variable power consumption" requirement into the claim. According to claim 1, each of the power islands has a power consumption "adapted to be independently controlled" (Ex. 1001, 13:27–28), but *controlled* power consumption is not the same thing as *variable* power consumption. If power consumption is maintained at a constant level, then power consumption is being controlled. I see nothing the Specification or the claim that requires each power island to have a variable power consumption.

The '811 Patent discloses: "The power manager 120 can dynamically change the power consumption of the power islands 112, 114, 116, and 118 based on the needs and operation of the integrated circuit 110." *Id.* at 4:34–37. That sentence is a description of the preferred embodiment and should not be read into the claim. *Luminara Worldwide, LLC v. Liown Elecs. Co.*, 814 F.3d 1343, 1353 (Fed. Cir. 2016) ("Absent lexicography or disavowal, we do not depart from the plain meaning of the claims.") Moreover, the preceding sentence explains that the power manager needs to change the power level for only "*one* of the power islands 112, 114, 116, and 118." Ex. 1001, 4:25–34 (emphasis added).

The concurrence's interpretation is inconsistent with claim 1, which recites that "each of the power consumptions adapted to be independently

controlled" and "at least one of the power islands [is] adapted to have the power manager control its associated power consumption" by selecting a threshold transistor voltage and by changing a frequency of operation or changing a supply voltage. Ex. 1001, 13:27–38 (limitations [1b], [1d]). In other words, although each of the power islands needs to have a power consumption that is independently controlled, *only one* of the power islands needs to have a power consumption that can be varied by changing the threshold voltage and either the frequency or supply voltage.

Furthermore, even if the concurrence were correct that each power island is required to have a variable power consumption, that is not a sufficient reason to reject the Petition. Although three of Nowka's four domains may have a constant supply voltage, constant voltage does not equate to constant power consumption. As is clear from claim 1, power consumption can be changed by changing other variables, such as threshold voltage or operating frequency. The concurrence bases its claim interpretation on the '811 Patent's description of the power manager. Con. 2–4. But the concurrence does not address Petitioner's contentions for limitation [1d] that recites the functions of the power manager. Petitioner contends that "Nowka discloses the actions of changing the frequency of operation or changing the supply voltage." Pet. 22–23 (citing Ex. 1004, 1442, 1444). The cited disclosures in Nowka pertain to controlling power consumption of the entire SOC, not just the logic domain. Ex. 1004, 1444 (describing effects on power consumption of dynamic voltage and frequency scaling).

Most of Patent Owner's arguments for limitation [1b] and Nowka rely on a claim construction for "power islands" that is inconsistent with the

Specification's definition of that term, as discussed above. Prelim. Resp. 23–27. I address Patent Owner's additional arguments below.

I disagree with Patent Owner's argument that Petitioner concedes in IPR2024-00719 that Nowka does not disclose a plurality of power islands. Prelim. Resp. 23. Patent Owner quotes Petitioner's assertion that Nowka "discloses a single variable power domain." *Id.* (quoting IPR2024-00719, Paper 2, 16). I do not interpret Petitioner's assertion as a concession that Nowka's other three domains are not power islands. On the contrary, Petitioner plainly contends that all four of Nowka's domains are power islands. Pet. 16; *see also* Prelim. Resp. 24 (acknowledging Petitioner's contention).

Patent Owner argues that, even if no claim construction is adopted, the description of a "power island" in the '811 Patent "focuses on whether (and how) 'power consumption is controlled within' a section of circuitry ... - not whether a section of circuitry receives a 'separate voltage supply." Prelim. Resp. 25–26 (citing Ex. 1001, 3:59–62; Pet. 16). I disagree. The '811 Patent states that "power consumption is controlled within" the power island, not that the *control* of power consumption is within the power island. Ex. 1001, 3:59–62 (emphasis added). Both the Specification and claims of the '811 Patent disclose external control of a power island's power consumption. For example, Figure 1 "depicts the power manager 120 as being located outside the integrated circuit 110" that includes power islands 112, 114, 116, and 118. Id. at 3:53–55, 4:44–46, Fig. 1. Figure 2 shows power management control layer (PMCL) 218, master power manager (MPM) 280, and smart power unit (SPU) 290 external to power islands 260 and 270. Id. at 4:61–5:6, Fig. 2. Figure 7 illustrates external voltage control circuitry 700, where the circuitry is external to integrated circuit 250 of

Figure 2. *Id.* at 8:38–52. Dependent claims 4 and 5 recite that "the system is configured to have the supply voltage provided by an external regulator" and "the external regulator is configured to be controlled by the power manager." *Id.* at 13:45–49.

For these reasons, I would find that Petitioner makes an adequate showing for claim limitation [1b] based on Nowka alone.

# 2. Limitation [1b]—Borkar

I agree with my colleagues that, although Petitioner contends that Borkar teaches limitation [1b], Petitioner does not explain how or why a POSITA would have combined that teaching with Nowka. Maj. 21–22; Con. 1–2; Pet. 17–19; Prelim. Resp. 30–32.

# 3. Limitation [1d]—Nowka and Borkar

Claim element [1d] recites:

at least one of the power islands adapted to have the power manager control its associated power consumption by a) the at least one of the power islands being configured to have one of plural threshold voltages of variable threshold transistors selected, and b) the system being configured to perform, during operation, an action on the at least one of the power islands, the action including changing a frequency of operation or changing a supply voltage.

Ex. 1001, 13:30–38.

Petitioner contends that the Nowka-Borkar combination renders obvious claim element [1d]. Pet. 21–23. Petitioner asserts that "Borkar discloses controlling power consumption of a power island by selecting a threshold voltage, as well as changing a frequency of operation or supply voltage during operation" and that "Nowka discloses the actions of changing the frequency of operation or changing the supply voltage." Pet. 22–23 (citing Ex. 1004, 1442, 1444, 1445; Ex. 1006, 3:46–57, 4:26–28, 5:25–34, 6:15–24, 6:31–40, 12:39–42). Petitioner cross-references its earlier discussion of motivation to combine Nowka and Borkar. Pet. 22.

Patent Owner disputes Petitioner's contentions for claim element [1d], focusing on the threshold voltage limitation. Prelim. Resp. 12–16. By way of summary, Patent Owner argues that "Petitioner has not shown that this [change of threshold voltage in Borkar] controls power consumption in a power island or, even if it did, that it is performed by the 'power manager' suggested by Petitioner in Borkar or the Nowka-Borkar combination." *Id.* at 16.

Patent Owner correctly observes that Petitioner relies upon Borkar to teach the threshold voltage limitation of claim element [1d]. Prelim. Resp. 12; *see* Pet. 13 ("Nowka does not explicitly disclose changing a threshold voltage to control the power consumption."); Pet. 22 ("Borkar discloses controlling power consumption of a power island by selecting a threshold voltage . . . .").

For claim element [1d], Petitioner relies on the following disclosure in Borkar:

In some embodiments, when the battery level signal is below a certain level, the supply voltage is lowered, the frequency of a processor clock is lowered, and/or the bias signals are changed to raise the threshold voltages of some or all of the transistors. This will reduce the power consumption to maintain the battery.

Ex. 1006, 5:25–30 (quoted at Pet 22).

Patent Owner argues that Petitioner's discussion of claim element [1d], including the above-quoted disclosure, "is unmoored from its prior discussion of and what it identified as a 'power island' in Borkar." Prelim. Resp. 12–13. I disagree. Addressing the "power islands" of claim

element [1b], Petitioner contends that "Borkar discloses multiple 'domains,' or groups of transistors, which have distinct power parameters." Pet. 17 (citing Ex. 1006, 9:19–24, 9:48–52, 9:58–59, 10:34–39, Figs. 5, 7). In view of Petitioner's contention that Borkar's "groups of transistors" are "power islands" (*id.*), I see a sufficient connection to Petitioner's contention for claim element [1d], which quotes Borkar's disclosure about controlling power consumption by raising "the threshold voltages of some or all of the transistors." Pet. 22.

Next, Patent Owner argues that Petitioner does not explain "how the power consumption would be controlled by a 'power manager' in Borkar (or Nowka, for that matter)." Prelim. Resp. 15. I disagree. As discussed above, Patent Owner does not dispute Petitioner's contention for claim element [1c] that a "power manager" is taught by Nowka's "on-chip supervisor" and "system software" and by Borkar's "control circuitry." *Id.*; Pet. 20–21. Patent Owner also does not dispute Petitioner's contention that Nowka's "on-chip supervisor" and "system software" control power consumption and that Borkar's "control circuitry" also controls power consumption. Prelim. Resp. 15; Pet. 20–21. Although Patent Owner argues that "Petitioner fails to explain how a POSITA would modify Nowka's 'on-chip supervisor' and 'system software' to select a threshold voltage" (Prelim. Resp. 15), I would find that Petitioner's contentions about combining Nowka with Borkar's teaching about threshold voltage are sufficient for purposes of institution. Pet. 13, 21–22.

Next, Patent Owner argues that "Petitioner does not and cannot show that Borkar's 'control circuitry' actually selects a 'threshold voltage' for a power island." Prelim. Resp. 16. I disagree. Patent Owner acknowledges that Borkar's control circuitry 262 provides various signals to the domains,

including "body bias signal(s)." *Id.* (citing Ex. 1006, 11:40–43). Although Patent Owner argues that "selecting 'one of plural threshold voltages of variable threshold transistors" is missing from this description, that argument overlooks the relationship between body bias and threshold of a transistor, as disclosed by Borkar. Ex. 1006, 3:34–36, 3:46–49 (explaining how body bias affects threshold voltage of transistor).

For these reasons, I would find that Petitioner makes an adequate showing for claim limitation [1d] based on Nowka and Borkar.

#### *4. Preamble and Limitations* [1a] and [1c]

Petitioner contends that the Nowka-Borkar combination renders obvious the claim 1 preamble, which recites "A system." Ex. 1001, 13:25; Pet. 14 (citing Ex. 1004, 1441; Ex. 1006, 1:59–60, 2:13–36, 2:61–65, 4:60–64, 5:1–2, Figs. 1, 5). Petitioner contends that Nowka and Borkar each disclose an integrated circuit, as recited in limitation [1a]. Ex. 1001, 13:25; Pet. 14–15 (citing Ex. 1004, Abstract, Fig. 1; Ex. 1006, 2:49–60). Patent Owner does not dispute Petitioner's contentions for the claim 1 preamble or limitation [1a].

Claim element [1c] recites "a power manager to control the power consumptions." Ex. 1001, 13:29. Petitioner contends that the Nowka-Borkar combination renders obvious limitation [1c]. Pet. 20–21. Petitioner contends that "Nowka discloses a 'power manager' comprised of an 'onchip supervisor' and 'system software." Pet. 20 (citing Ex. 1004, 1442, 1446). Petitioner contends that Borkar discloses control circuitry for controlling settings of a supply voltage signal and a clock signal and that a "POSITA would have understood Borkar's 'control circuitry' to be a power manager because it controls the power consumption of the relevant

processor(s) or domain(s)." Pet. 20–21 (citing Ex. 1003 ¶ 68; Ex. 1006, 1:63–2:1; 2:63–3:11, 4:3–11, 4:20–33, 5:47–64, 6:12–53, 11:25–67, Figs. 1– 5, 7).

Patent Owner does not specifically dispute Petitioner's contentions for limitation [1c]. *See* Prelim. Resp. 15 (paraphrasing Petitioner's contentions for claim element [1c] in the context of disputing Petitioner's contentions for claim element [1d]).

I would find that Petitioner's contentions for the preamble and limitations [1a] and [1c], as summarized, are sufficiently supported by the cited evidence and adequate for purposes of institution.

# 5. Conclusion

For the reasons discussed above, it is my view that Petitioner shows a reasonable likelihood of prevailing on its challenge to independent claim 1 based on Nowka and Borkar, and I respectfully dissent from the denial of institution.

# For PETITIONER:

Timothy W. Riffe Joseph Colaianni Linhong Zhang Jared M. Hartzman FISH & RICHARDSON P.C. riffe@fr.com colaianni@fr.com lwzhang@fr.com hartzman@fr.com

For PATENT OWNER:

Kenneth J. Weatherwax Flavio M. Rose LOWENSTEIN & WEATHERWAX LLP weatherwax@lowensteinweatherwax.com rose@lowensteinweatherwax.com